製品カテゴリ

商品のタグ

FMUSERサイト

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net ->アフリカーンス語

- sq.fmuser.net ->アルバニア語

- ar.fmuser.net ->アラビア語

- hy.fmuser.net ->アルメニア語

- az.fmuser.net ->アゼルバイジャン

- eu.fmuser.net ->バスク

- be.fmuser.net ->ベラルーシ語

- bg.fmuser.net ->ブルガリア語

- ca.fmuser.net ->カタロニア語

- zh-CN.fmuser.net ->中国語(簡体字)

- zh-TW.fmuser.net ->中国語(繁体字)

- hr.fmuser.net ->クロアチア語

- cs.fmuser.net ->チェコ

- da.fmuser.net ->デンマーク語

- nl.fmuser.net ->オランダ語

- et.fmuser.net ->エストニア語

- tl.fmuser.net ->フィリピン人

- fi.fmuser.net ->フィンランド語

- fr.fmuser.net ->フランス語

- gl.fmuser.net ->ガリシア語

- ka.fmuser.net ->グルジア語

- de.fmuser.net ->ドイツ語

- el.fmuser.net ->ギリシャ語

- ht.fmuser.net ->ハイチクレオール

- iw.fmuser.net ->ヘブライ語

- hi.fmuser.net ->ヒンディー語

- hu.fmuser.net ->ハンガリー語

- is.fmuser.net ->アイスランド語

- id.fmuser.net ->インドネシア語

- ga.fmuser.net ->アイルランド

- it.fmuser.net ->イタリア語

- ja.fmuser.net ->日本語

- ko.fmuser.net ->韓国語

- lv.fmuser.net ->ラトビア語

- lt.fmuser.net ->リトアニア語

- mk.fmuser.net ->マケドニア語

- ms.fmuser.net ->マレー語

- mt.fmuser.net ->マルタ語

- no.fmuser.net ->ノルウェー語

- fa.fmuser.net ->ペルシア語

- pl.fmuser.net ->ポーランド語

- pt.fmuser.net ->ポルトガル語

- ro.fmuser.net ->ルーマニア語

- ru.fmuser.net ->ロシア語

- sr.fmuser.net ->セルビア語

- sk.fmuser.net ->スロバキア

- sl.fmuser.net ->スロベニア語

- es.fmuser.net ->スペイン語

- sw.fmuser.net ->スワヒリ語

- sv.fmuser.net ->スウェーデン語

- th.fmuser.net ->タイ

- tr.fmuser.net ->トルコ語

- uk.fmuser.net ->ウクライナ語

- ur.fmuser.net ->ウルドゥー語

- vi.fmuser.net ->ベトナム人

- cy.fmuser.net ->ウェールズ

- yi.fmuser.net ->イディッシュ語

PNGおよびNMOSトランジスタ

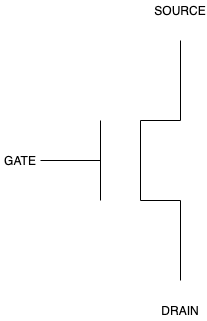

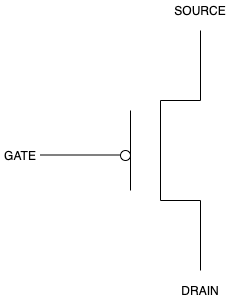

マイクロプロセッサはトランジスタで構成されています。 特に、MOSトランジスタで構成されています。 MOSはMetal-OxideSemiconductorの頭字語です。 MOSトランジスタには、pMOS(正のMOS)とnMOS(負のMOS)のXNUMX種類があります。 すべてのpMOSおよびnMOSには、ゲート、ソース、およびドレインのXNUMXつの主要コンポーネントが装備されています。

pMOSとnMOSがどのように動作するかを正しく理解するには、最初にいくつかの用語を定義することが重要です。

閉回路:これは、電気がゲートからソースに流れていることを意味します。

開回路:これは、電気がゲートからソースに流れていないことを意味します。 むしろ、電気はゲートからドレインに流れています。

nMOSトランジスタが無視できない電圧を受け取ると、ソースからドレインへの接続がワイヤとして機能します。 電気は抑制されずにソースからドレインに流れます—これは閉回路と呼ばれます。 一方、nMOSトランジスタが0ボルト付近の電圧を受け取ると、ソースからドレインへの接続が切断され、これは開回路と呼ばれます。

p型トランジスタはn型トランジスタとは正反対に機能します。 電圧が無視できない場合、nMOSはソースと閉回路を形成しますが、電圧が無視できない場合、pMOSはソースと開回路を形成します。

上に示したpMOSトランジスタの画像でわかるように、pMOSトランジスタとnMOSトランジスタの唯一の違いは、ゲートと最初のバーの間の小さな円です。 この円は、電圧から値を反転します。 したがって、ゲートが値1を表す電圧を送信すると、インバータは1を0に変更し、それに応じて回路を機能させます。

pMOSとnMOSは、両方をXNUMXつの巨大なMOS回路に結合すると、逆に、つまり相補的に機能するため、cMOS回路と呼ばれ、相補型金属酸化膜半導体の略です。

MOS回路の活用

pMOS回路とnMOS回路を組み合わせて、GATESと呼ばれるより複雑な構造、より具体的には論理ゲートを構築できます。 これらの論理関数の概念とそれに関連する真理値表については、前のブログですでに紹介しました。クリックすると表示されます。 ここ.

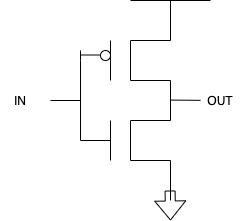

ソースに接続するpMOSトランジスタとグランドに接続するnMOSトランジスタを接続できます。 これは、cMOSトランジスタの最初の例になります。

このcMOSトランジスタは、NOT論理関数と同様に機能します。

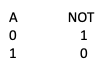

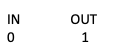

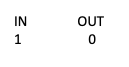

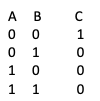

NOT真理値表を見てみましょう:

NOT真理値表では、すべての入力値:Aが反転されます。 上記の回路はどうなりますか?

さて、入力が0であると想像してみましょう。

0は、pMOS(上)とnMOS(下)の両方に接続され、ワイヤを上下に移動します。 値0がpMOSに達すると、1に反転されます。 したがって、ソースへの接続は閉じられます。 これにより、アース(排水路)への接続も閉じられていない限り、論理値1が生成されます。 トランジスタは相補的であるため、nMOSトランジスタは値を反転させないことがわかります。 したがって、値0をそのまま使用し、グラウンド(ドレイン)への開回路を作成します。 したがって、ゲートの論理値1が生成されます。

1がIN値の場合はどうなりますか? 上記と同じ手順に従って、値1がpMOSとnMOSの両方に送信されます。 値がpMOSによって受信されると、値は0に反転されます。 したがって、SOURCEへの接続は開いています。 値がnMOSによって受信されるとき、値は反転されません。 したがって、値は1のままです。nMOSが値1を受信すると、接続は閉じられます。 そのため、アースへの接続は閉じられます。 これにより、論理値0が生成されます。

XNUMXセットの入力/出力を組み合わせると次のようになります。

この真理値表が論理関数NOTが生成するものとまったく同じであることは非常に簡単にわかります。 したがって、これはNOTゲートとして知られています。

これらのXNUMXつの単純なトランジスタを使用して、より複雑な構造を作成できますか? 絶対! 次に、NORゲートとORゲートを作成します。

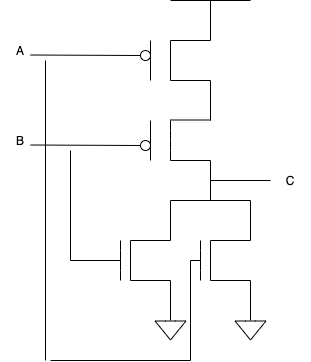

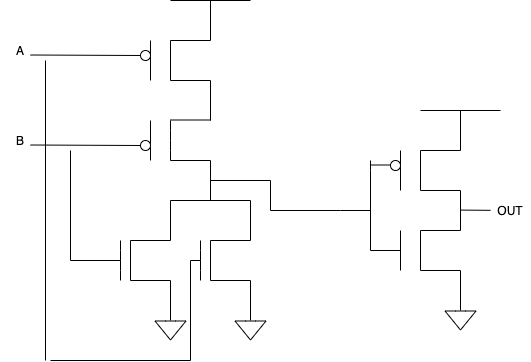

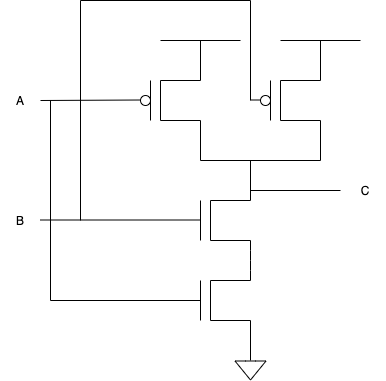

この回路は、上部にXNUMXつのpMOSトランジスタを使用し、下部にXNUMXつのnMOSトランジスタを使用します。 繰り返しになりますが、ゲートへの入力を見て、ゲートがどのように動作するかを確認しましょう。

Aが0でBが0の場合、このゲートは、pMOSトランジスタに到達したときに両方の値を1に反転します。 ただし、nMOSトランジスタは両方とも値0を維持します。これにより、ゲートは値1を生成します。

Aが0でBが1の場合、このゲートはpMOSトランジスタに到達したときに両方の値を反転します。 したがって、Aは1に変更され、Bは0に変更されます。これはソースにつながりません。 入力をソースに接続するために、両方のトランジスタが閉回路を必要とするためです。 nMOSトランジスタは値を反転しません。 したがって、Aに関連付けられたnMOSは0を生成し、Bに関連付けられたnMOSは1を生成します。 したがって、Bに関連付けられたnMOSは、グランドへの閉回路を生成します。 これにより、ゲートは値0を生成します。

Aが1でBが0の場合、このゲートはpMOSトランジスタに到達したときに両方の値を反転します。 したがって、Aは0に変更され、Bは1に変更されます。これはソースにつながりません。 入力をソースに接続するために、両方のトランジスタが閉回路を必要とするためです。 nMOSトランジスタは値を反転しません。 したがって、Aに関連付けられたnMOSは1を生成し、Bに関連付けられたnMOSは0を生成します。 したがって、Awillに関連付けられたnMOSは、グランドへの閉回路を生成します。 これにより、ゲートは0の値を生成します。

Aが1でBが1の場合、このゲートはpMOSトランジスタに到達したときに両方の値を反転します。 したがって、Aは0に変更され、Bは0に変更されます。これはソースにつながりません。 入力をソースに接続するために、両方のトランジスタが閉回路を必要とするためです。 nMOSトランジスタは値を反転しません。 したがって、Aに関連付けられたnMOSは1を生成し、Bに関連付けられたnMOSは1を生成します。 したがって、Aに関連付けられたnMOSとBに関連付けられたnMOSは、グランドへの閉回路を生成します。 これにより、ゲートは0の値を生成します。

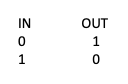

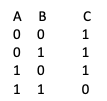

したがって、ゲートの真理値表は次のようになります。

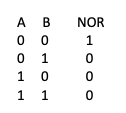

一方、NOR論理関数の真理値表は次のとおりです。

したがって、このゲートは、真理値表をNOR論理関数と共有しているため、NORゲートであることが確認されました。

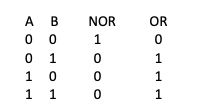

ここで、これまでに作成した両方のゲートを組み合わせて、ORゲートを作成します。 NORはNOTORの略です。 したがって、すでに反転されているゲートを反転すると、元のゲートに戻ります。 実際に動作することを確認するために、これをテストしてみましょう。

ここで行ったことは、以前からNORゲートを取得し、出力にNOTゲートを適用したことです。 上に示したように、NOTゲートは値1を取り、0を出力し、NOTゲートは値0を取り、1を出力します。

これにより、NORゲートの値が取得され、すべての0が1に、1が0に変換されます。 したがって、真理値表は次のようになります。

これらのゲートをテストする練習をもっとしたい場合は、上記の値を自分で試してみて、ゲートが同等の結果を生成することを確認してください。

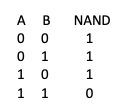

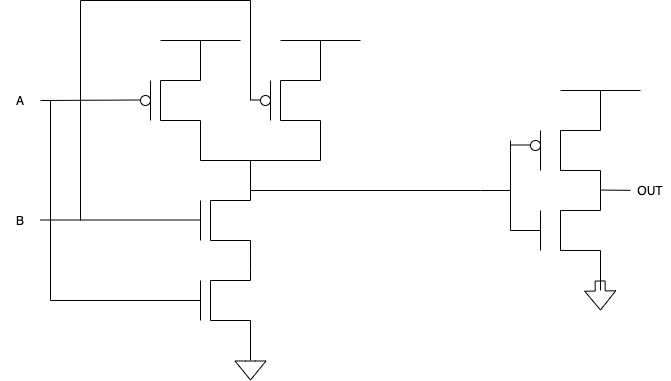

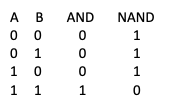

これはNANDゲートであると主張しますが、このゲートの真理値表をテストして、実際にNANDゲートであるかどうかを判断しましょう。

Aが0でBが0の場合、AのpMOSは1を生成し、AのnMOSは0を生成します。 したがって、このゲートは、閉回路でソースに接続され、開回路でグランドから切断されるため、論理1を生成します。

Aが0でBが1の場合、AのpMOSは1を生成し、AのnMOSは0を生成します。 したがって、このゲートは、閉回路でソースに接続され、開回路でグランドから切断されるため、論理1を生成します。

Aが1でBが0の場合、BのpMOSは1を生成し、BのnMOSは0を生成します。 したがって、このゲートは、閉回路でソースに接続され、開回路でグランドから切断されるため、論理1を生成します。

Aが1でBが1の場合、AのpMOSは0を生成し、AのnMOSは1を生成します。 したがって、BのpMOSとnMOSもチェックする必要があります。 BのpMOSは0を生成し、BのnMOSは1を生成します。 したがって、このゲートは、開回路でソースから切断され、閉回路でグランドに接続されるため、論理0を生成します。

真理値表は次のとおりです。

一方、NAND論理関数の真理値表は次のとおりです。

したがって、これが実際にNANDゲートであることを確認しました。

では、どのようにしてANDゲートを構築するのでしょうか。 さて、NORゲートからORゲートを作成したのとまったく同じ方法で、ANDゲートを作成します。 インバーターを取り付けます!

NANDゲートの出力にNOT関数が適用されているため、真理値表は次のようになります。

繰り返しになりますが、私があなたに言っていることが真実であることを確認してください。

今日は、pMOSおよびnMOSトランジスタとは何か、およびそれらを使用してより複雑な構造を構築する方法について説明しました。 このブログがお役に立てば幸いです。 私の以前のブログを読みたい場合は、以下のリストがあります。