製品カテゴリ

商品のタグ

FMUSERサイト

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net ->アフリカーンス語

- sq.fmuser.net ->アルバニア語

- ar.fmuser.net ->アラビア語

- hy.fmuser.net ->アルメニア語

- az.fmuser.net ->アゼルバイジャン

- eu.fmuser.net ->バスク

- be.fmuser.net ->ベラルーシ語

- bg.fmuser.net ->ブルガリア語

- ca.fmuser.net ->カタロニア語

- zh-CN.fmuser.net ->中国語(簡体字)

- zh-TW.fmuser.net ->中国語(繁体字)

- hr.fmuser.net ->クロアチア語

- cs.fmuser.net ->チェコ

- da.fmuser.net ->デンマーク語

- nl.fmuser.net ->オランダ語

- et.fmuser.net ->エストニア語

- tl.fmuser.net ->フィリピン人

- fi.fmuser.net ->フィンランド語

- fr.fmuser.net ->フランス語

- gl.fmuser.net ->ガリシア語

- ka.fmuser.net ->グルジア語

- de.fmuser.net ->ドイツ語

- el.fmuser.net ->ギリシャ語

- ht.fmuser.net ->ハイチクレオール

- iw.fmuser.net ->ヘブライ語

- hi.fmuser.net ->ヒンディー語

- hu.fmuser.net ->ハンガリー語

- is.fmuser.net ->アイスランド語

- id.fmuser.net ->インドネシア語

- ga.fmuser.net ->アイルランド

- it.fmuser.net ->イタリア語

- ja.fmuser.net ->日本語

- ko.fmuser.net ->韓国語

- lv.fmuser.net ->ラトビア語

- lt.fmuser.net ->リトアニア語

- mk.fmuser.net ->マケドニア語

- ms.fmuser.net ->マレー語

- mt.fmuser.net ->マルタ語

- no.fmuser.net ->ノルウェー語

- fa.fmuser.net ->ペルシア語

- pl.fmuser.net ->ポーランド語

- pt.fmuser.net ->ポルトガル語

- ro.fmuser.net ->ルーマニア語

- ru.fmuser.net ->ロシア語

- sr.fmuser.net ->セルビア語

- sk.fmuser.net ->スロバキア

- sl.fmuser.net ->スロベニア語

- es.fmuser.net ->スペイン語

- sw.fmuser.net ->スワヒリ語

- sv.fmuser.net ->スウェーデン語

- th.fmuser.net ->タイ

- tr.fmuser.net ->トルコ語

- uk.fmuser.net ->ウクライナ語

- ur.fmuser.net ->ウルドゥー語

- vi.fmuser.net ->ベトナム人

- cy.fmuser.net ->ウェールズ

- yi.fmuser.net ->イディッシュ語

半加算器とは:回路図とそのアプリケーション

Date:2021/10/18 21:55:58 Hits:

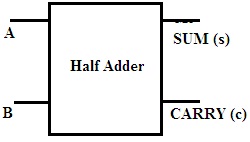

ハーフアダーは一種の基本的なデジタル回路です。 以前は、アナログ回路で実行されるさまざまな操作があります。 デジタル電子機器の発見後、同様の操作がデジタル電子機器で実行されます。 デジタルシステムは効果的で信頼できると考えられています。 さまざまな操作の中で、最も顕著な操作の3つは算術です。 これには、加算、減算、乗算、および除算が含まれます。 しかし、それがコンピュータである可能性があることはすでに知られています。電卓のような電子機器は数学的な操作を実行できます。 これらの操作はバイナリ値で構成されて実行されます。これは、特定の回路が含まれているために可能です。 これらの回路は、バイナリ加算器および減算器と呼ばれます。 このタイプの回路は、バイナリコード、Excess-0コード、およびその他のコード用に設計されています。 さらに、バイナリ加算器は1つのタイプに分類されます。 半加算器と全加算器半加算器とは1進数の加算を実行するように機能するデジタル電子回路を半加算器と定義します。 加算のプロセスは否定的です。唯一の違いは、選択された記数法です。 0進数システムには1と0しか存在しません。 数値の重みは、完全にXNUMX進数の位置に基づいています。 これらのXNUMXとXNUMXのうち、XNUMXが最大の桁として扱われ、XNUMXが小さい桁として扱われます。 この加算器のブロック図は次のとおりです。 半加算器半加算器の回路図半加算器はXNUMXつの入力で構成され、XNUMXつの出力を生成します。 それは最も単純なデジタル回路であると考えられています。 この回路への入力は、加算が実行されるビットです。 得られる出力は合計とキャリーです。

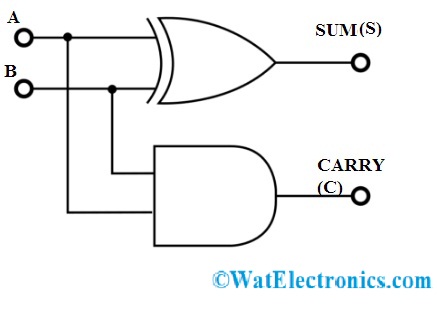

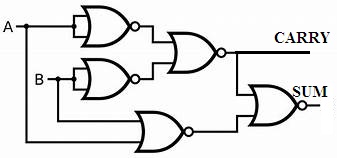

半加算器半加算器の回路図半加算器はXNUMXつの入力で構成され、XNUMXつの出力を生成します。 それは最も単純なデジタル回路であると考えられています。 この回路への入力は、加算が実行されるビットです。 得られる出力は合計とキャリーです。  半加算器この加算器の回路はXNUMXつのゲートで構成されています。 それらはANDゲートとXORゲートです。 適用される入力は、回路に存在する両方のゲートで同じです。 ただし、出力は各ゲートから取得されます。 XORゲートの出力はSUMと呼ばれ、ANDの出力はCARRYと呼ばれます。半加算器の真理値表得られた出力と適用された入力の関係を取得するには、真理値表と呼ばれるテーブルを使用して分析できます。

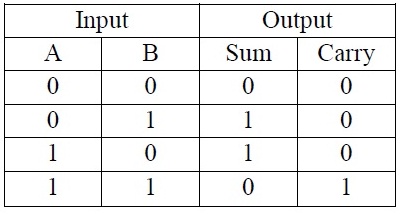

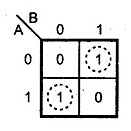

半加算器この加算器の回路はXNUMXつのゲートで構成されています。 それらはANDゲートとXORゲートです。 適用される入力は、回路に存在する両方のゲートで同じです。 ただし、出力は各ゲートから取得されます。 XORゲートの出力はSUMと呼ばれ、ANDの出力はCARRYと呼ばれます。半加算器の真理値表得られた出力と適用された入力の関係を取得するには、真理値表と呼ばれるテーブルを使用して分析できます。 半加算真理値表上記の真理値表から、ポイントは次のように明らかです。A= 0の場合、両方の入力が適用されるB = 0は0です。次に、出力SUMとCARRYの両方が0です。入力が1の場合、SUMはb e1になりますが、CARRYは0になります。両方の入力が1の場合、SUMは0に等しく、CARRYは1に等しくなります。適用された入力に基づいて、半加算器は演算を続行します。方程式このタイプの回路の方程式は、積和(SOP)と和積(POS)の概念によって実現できます。 このタイプの回路のブール方程式は、適用された入力と取得された出力の間の関係を決定します。方程式を決定するために、kマップは真理値表の値に基づいて描画されます。 XNUMXつの論理ゲートが使用されているため、XNUMXつの方程式で構成されています。キャリーのkマップは次のとおりです。

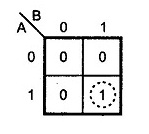

半加算真理値表上記の真理値表から、ポイントは次のように明らかです。A= 0の場合、両方の入力が適用されるB = 0は0です。次に、出力SUMとCARRYの両方が0です。入力が1の場合、SUMはb e1になりますが、CARRYは0になります。両方の入力が1の場合、SUMは0に等しく、CARRYは1に等しくなります。適用された入力に基づいて、半加算器は演算を続行します。方程式このタイプの回路の方程式は、積和(SOP)と和積(POS)の概念によって実現できます。 このタイプの回路のブール方程式は、適用された入力と取得された出力の間の関係を決定します。方程式を決定するために、kマップは真理値表の値に基づいて描画されます。 XNUMXつの論理ゲートが使用されているため、XNUMXつの方程式で構成されています。キャリーのkマップは次のとおりです。  K-Map AND Gate CARRYの出力式は、ANDゲートから取得されます。C= A.BSUMのブール式は、SOP形式で実現されます。 したがって、SUMのKマップは次のようになります。

K-Map AND Gate CARRYの出力式は、ANDゲートから取得されます。C= A.BSUMのブール式は、SOP形式で実現されます。 したがって、SUMのKマップは次のようになります。 K-Map for Sum(XOR)決定された式は次のとおりです。S=A⊕Bアプリケーションこの基本的な加算器のアプリケーションは次のとおりです。バイナリビットで加算を実行するには、コンピュータに存在する算術論理演算装置がこの加算回路を優先します。半加算回路の組み合わせにより、これらの論理回路は、計算機の設計に適しています。アドレスとテーブルを計算するには、これらの回路を使用します。これらの回路は、加算だけでなく、デジタル回路のさまざまなアプリケーションを処理できます。 さらに、これがデジタルエレクトロニクスの心臓部になります。VHDLコード半加算器回路のVHDLコードislibrary ieee; use ieee.std_logic_1164.all; entity half_adder isport(a、b:in bit; sum、carry:out bit); end half_adder ; half_adderのアーキテクチャデータisbeginsum <= a xor b;キャリー<= aおよびb;終了データ; FAQ1。 加算器とはどういう意味ですか?加算を実行することを唯一の目的とするデジタル回路は、加算器として知られています。 これらはALUの主要コンポーネントです。 加算器は、さまざまな形式の数値に加えて動作します。 加算器の出力は合計とキャリーです。 半加算器の制限は何ですか?前のビットから生成されたキャリービットは追加できませんが、この加算器の制限です。 複数ビットの加算を実行するには、これらの回路を優先することはできません。 NORゲートを使用して半加算器を実装する方法このタイプの加算器の実装は、NORゲートを使用して実行することもできます。 これは別のユニバーサルゲートです。

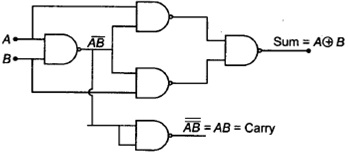

K-Map for Sum(XOR)決定された式は次のとおりです。S=A⊕Bアプリケーションこの基本的な加算器のアプリケーションは次のとおりです。バイナリビットで加算を実行するには、コンピュータに存在する算術論理演算装置がこの加算回路を優先します。半加算回路の組み合わせにより、これらの論理回路は、計算機の設計に適しています。アドレスとテーブルを計算するには、これらの回路を使用します。これらの回路は、加算だけでなく、デジタル回路のさまざまなアプリケーションを処理できます。 さらに、これがデジタルエレクトロニクスの心臓部になります。VHDLコード半加算器回路のVHDLコードislibrary ieee; use ieee.std_logic_1164.all; entity half_adder isport(a、b:in bit; sum、carry:out bit); end half_adder ; half_adderのアーキテクチャデータisbeginsum <= a xor b;キャリー<= aおよびb;終了データ; FAQ1。 加算器とはどういう意味ですか?加算を実行することを唯一の目的とするデジタル回路は、加算器として知られています。 これらはALUの主要コンポーネントです。 加算器は、さまざまな形式の数値に加えて動作します。 加算器の出力は合計とキャリーです。 半加算器の制限は何ですか?前のビットから生成されたキャリービットは追加できませんが、この加算器の制限です。 複数ビットの加算を実行するには、これらの回路を優先することはできません。 NORゲートを使用して半加算器を実装する方法このタイプの加算器の実装は、NORゲートを使用して実行することもできます。 これは別のユニバーサルゲートです。 NORゲートを使用したハーフアダー4。 NANDゲートを使用して半加算器を実装する方法NANDゲートはユニバーサルゲートの一種です。 これは、NANDゲートを使用することであらゆる種類の回路設計が可能であることを示しています。

NORゲートを使用したハーフアダー4。 NANDゲートを使用して半加算器を実装する方法NANDゲートはユニバーサルゲートの一種です。 これは、NANDゲートを使用することであらゆる種類の回路設計が可能であることを示しています。 半加算器上記の回路から、一方のNANDゲートの出力をもう一方のNANDゲートとして入力に適用することにより、キャリー出力を生成できます。 これは、ANDゲートから得られる出力によく知られています。SUMの出力式は、最初のNANDゲートの出力とAおよびBの個々の入力をさらにNANDゲートに適用することで生成できます。 最後に、これらのNANDゲートによって得られた出力が再びゲートに適用されます。 したがって、SUMの出力が生成されます。したがって、デジタル回路の基本的な加算器は、さまざまな論理ゲートを使用して設計できます。 しかし、複数ビットの加算は複雑になり、半加算器の制限と見なされます。 どのICが実際のカウンタのインクリメント操作に使用されているか説明できますか?

半加算器上記の回路から、一方のNANDゲートの出力をもう一方のNANDゲートとして入力に適用することにより、キャリー出力を生成できます。 これは、ANDゲートから得られる出力によく知られています。SUMの出力式は、最初のNANDゲートの出力とAおよびBの個々の入力をさらにNANDゲートに適用することで生成できます。 最後に、これらのNANDゲートによって得られた出力が再びゲートに適用されます。 したがって、SUMの出力が生成されます。したがって、デジタル回路の基本的な加算器は、さまざまな論理ゲートを使用して設計できます。 しかし、複数ビットの加算は複雑になり、半加算器の制限と見なされます。 どのICが実際のカウンタのインクリメント操作に使用されているか説明できますか?

伝言を残す

メッセージ一覧

コメント読み込んでいます...